# 3.3V LOW SKEW PLL-BASED CMOS CLOCK DRIVER (WITH 3-STATE)

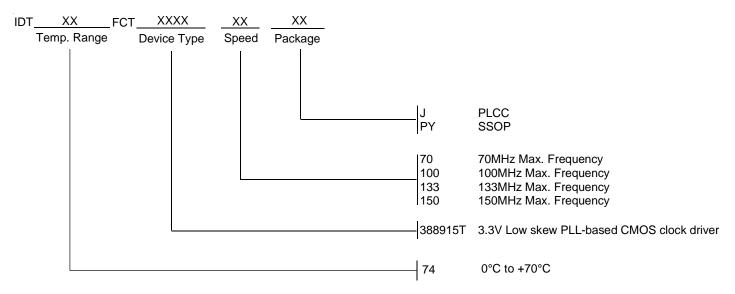

## IDT74FCT388915T 70/100/133/150

### FEATURES:

- 0.5 MICRON CMOS Technology

- Input frequency range: 10MHz f2Q Max. spec (FREQ\_SEL = HIGH)

- Max. output frequency: 150MHz

- Pin and function compatible with FCT88915T, MC88915T

- 5 non-inverting outputs, one inverting output, one 2x output, one ÷2 output; all outputs are TTL-compatible

- · 3-State outputs

- Duty cycle distortion < 500ps (max.)</li>

- 32/-16mA drive at CMOS output voltage levels

- VCC = 3.3V ± 0.3V

- · Inputs can be driven by 3.3V or 5V components

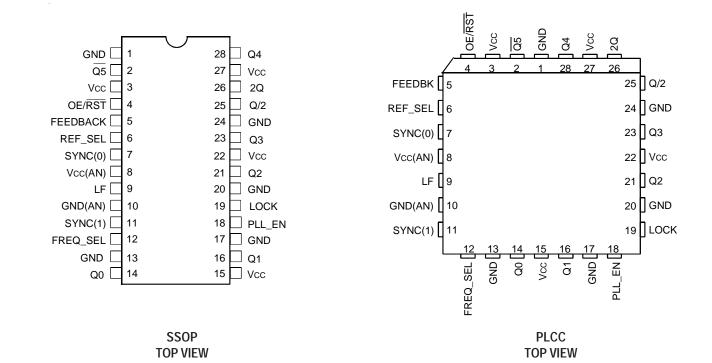

- Available in 28 pin PLCC and SSOP packages

# DESCRIPTION:

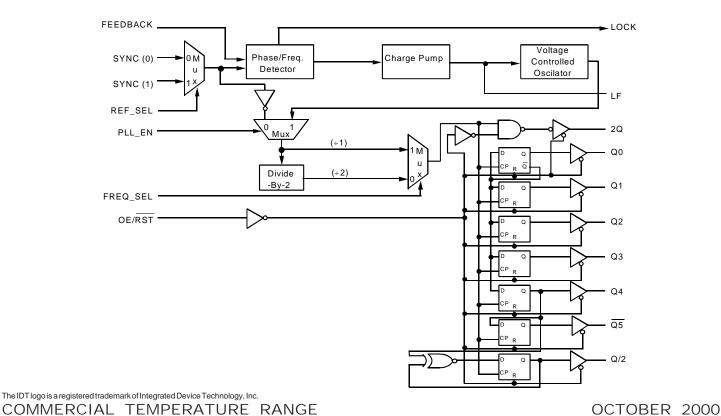

The FCT388915T uses phase-lock loop technology to lock the frequency and phase of outputs to the input reference clock. It provides low skew clock distribution for high performance PCs and workstations. One of the outputs is fed back to the PLL at the FEEDBACK input resulting in essentially zero delay across the device. The PLL consists of the phase/ frequency detector, charge pump, loop filter and VCO. The VCO is designed for a 2Q operating frequency range of 40MHz to f2Q Max.

The FCT388915T provides 8 outputs, the  $\overline{Q5}$  output is inverted from the Q outputs. The 2Q runs at twice the Q frequency and Q/2 runs at half the Q frequency.

The FREQ\_SEL control provides an additional  $\div$  2 option in the output path. PLL\_EN allows bypassing of the PLL, which is useful in static test modes. When PLL\_EN is low, SYNC input may be used as a test clock. In this test mode, the input frequency is not limited to the specified range and the polarity of outputs is complementary to that in normal operation (PLL\_EN = 1). The LOCK output attains logic HIGH when the PLL is in steady-state phase and frequency lock. When OE/RST is low, all the outputs are put in high impedance state and registers at Q, Q and Q/2 outputs are reset.

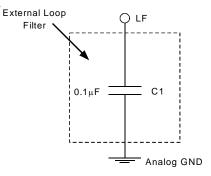

The FCT388915T requires one external loop filter component as recommended in Figure 3.

# FUNCTIONAL BLOCK DIAGRAM

DSC-4243/1

# **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| Pin Name | I/O | Description                                                                                                               |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------|

| SYNC(0)  | I   | Reference clock input                                                                                                     |

| SYNC(1)  | I   | Reference clock input                                                                                                     |

| REF_SEL  | I   | Chooses reference between SYNC (0) & SYNC (1) (refer to functional block diagram)                                         |

| FREQ_SEL | I   | Selects between ÷ 1 and ÷ 2 frequency options (refer to functional block diagram)                                         |

| FEEDBACK | I   | Feedback input to phase detector                                                                                          |

| LF       | I   | Input for external loop filter connection                                                                                 |

| Q0-Q4    | 0   | Clock output                                                                                                              |

| Q5       | 0   | Inverted clock output                                                                                                     |

| 2Q       | 0   | Clock output (2 x Q frequency)                                                                                            |

| Q/2      | 0   | Clock output (Q frequency ÷ 2)                                                                                            |

| LOCK     | 0   | Indicates phase lock has been achieved (HIGH when locked)                                                                 |

| OE/RST   | I   | Asynchronous reset (active LOW) and output enable (active HIGH). When HIGH, outputs are enabled. When LOW, outputs are in |

|          |     | HIGH impedance.                                                                                                           |

| PLL_EN   | I   | Disables phase-lock for low frequency testing (refer to functional block diagram)                                         |

COMMERCIALTEMPERATURERANGE

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol               | Description                          | Max             | Unit |  |

|----------------------|--------------------------------------|-----------------|------|--|

| VTERM <sup>(2)</sup> | Terminal Voltage with Respect to GND | -0.5 to +4.6    | V    |  |

| VTERM <sup>(3)</sup> | Terminal Voltage with Respect to GND | –0.5 to +7      | V    |  |

| VTERM <sup>(4)</sup> | Terminal Voltage with Respect to GND | -0.5 to Vcc+0.5 | V    |  |

| Tstg                 | Storage Temperature                  | -65 to +150     | °C   |  |

| Ιουτ                 | DC Output Current                    | -60 to +120     | mA   |  |

#### NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. Vcc terminals.

3. Input terminals.

4. Outputs and I/O terminals.

### CAPACITANCE (TA = +25°C, F = 1.0MHz)

| Symbol | Parameter          | Conditions | Тур. | Max. | Unit |

|--------|--------------------|------------|------|------|------|

| CIN    | Input Capacitance  | VIN = 0V   | 4.5  | 6    | pF   |

| Соит   | Output Capacitance | Vout = 0V  | 5.5  | 8    | pF   |

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: Commercial: TA =  $0^{\circ}$ C to + $70^{\circ}$ C, VCC = 3.3V ± 0.3V

| Symbol               | Parameter                                    | Test Condi                                 | tions <sup>(1)</sup>                                                     | Min.               | Тур. <sup>(2)</sup> | Max. | Unit |

|----------------------|----------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------|--------------------|---------------------|------|------|

| Vih                  | Input HIGH Level                             | Guaranteed Logic HIGH Level                |                                                                          | 2                  | —                   | _    | V    |

| VIL                  | Input LOW Level                              | Guaranteed Logic LOW Level                 |                                                                          | _                  | —                   | 0.8  | V    |

| Ін                   | Input HIGH Current <sup>(4)</sup>            | Vcc = Max.                                 | VI = 5.5V                                                                | _                  | -                   | ±1   | μA   |

| lil                  | Input LOW Current <sup>(4)</sup>             | Vcc = Max.                                 | VI = GND                                                                 | _                  | -                   | ±1   | μA   |

| lozh                 | High Impedance Output Current <sup>(4)</sup> | Vcc = Max.                                 | VI = VCC                                                                 | _                  | —                   | ±1   | μA   |

| lozl                 | (3-State Output Pins)                        | VI = GND                                   |                                                                          | _                  | _                   | ±1   |      |

| Vik                  | Clamp Diode Voltage                          | Vcc = Min., IIN = -18mA                    |                                                                          | _                  | -0.7                | -1.2 | V    |

| Iodh                 | Output Drive Current                         | VCC = Min., VIN = VIH or VIL, VO =         | $V_{CC} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}, V_{O} = 1.5 V^{(3)}$ |                    | —                   | _    | mA   |

| IODL                 | Output Drive Current                         | VCC = Min., VIN = VIH or VIL, VO =         | 1.5V <sup>(3)</sup>                                                      | 50                 | -                   | _    | mA   |

| Vон                  | Output HIGH Voltage                          | Vcc = Min                                  | Iон = –16mA                                                              | 2.4 <sup>(4)</sup> | 3.3                 | _    | V    |

| Vol                  | Output LOW Voltage                           | Vcc = Min                                  | Iol = 32mA                                                               | _                  | 0.3                 | 0.5  | V    |

| Vн                   | Input Hysteresis                             | _                                          |                                                                          | —                  | 100                 | —    | mV   |

| Iccl<br>Iccн<br>Iccz | Quiescent Power Supply Current               | Vcc = Max.,VIN = GND or Vcc<br>(Test Mode) |                                                                          | —                  | 2                   | 6    | μA   |

#### NOTES:

1. For conditions shown as Min. or Max., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 3.3V, +25°C ambient.

3. Not more than one output should be tested at one time. Duration of the test should not exceed one second.

4. VoH = Vcc - 0.6V at rated current.

# POWER SUPPLY CHARACTERISTICS

| Symbol | Parameter                                   | TestCond                            | litions <sup>(1)</sup>                | Min. | Тур.(2) | Max. | Unit |

|--------|---------------------------------------------|-------------------------------------|---------------------------------------|------|---------|------|------|

| ∆lcc   | Quiescent Power Supply Current              | Vcc = Max.                          | $VIN = VCC - 0.6V^{(3)}$              | _    | 2       | 30   | μA   |

|        | TTL Inputs HIGH                             | $VIN = VCC - 2.1V^{(3)}$            |                                       |      |         |      |      |

| ICCD   | Dynamic Power Supply Current <sup>(4)</sup> | Vcc = Max.                          | VIN = VCC                             | _    | 0.2     | 0.3  | mA/  |

|        |                                             | All Outputs Open                    | Vin = GND                             |      |         |      | MHz  |

| Cpd    | Power Dissipation Capacitance               | 50% Duty Cycle                      |                                       | _    | 15      | 25   | pF   |

| lc     | Total Power Supply Current <sup>(6)</sup>   | Vcc = Max.                          |                                       | _    | 30      | 60   | mA   |

|        |                                             | PLL_EN = 1, LOCK = 1, FEEDBACK = Q4 |                                       |      |         |      |      |

|        |                                             | SYNC frequency = 50MHz. All b       | bits loaded with 15pF                 |      |         |      |      |

|        |                                             | Vcc = Max.                          |                                       | —    | 90      | 120  | mA   |

|        |                                             | PLL_EN = 1, LOCK = 1, FEED          | BACK = Q4                             |      |         |      |      |

|        |                                             | SYNC frequency = 50MHz. All b       | bits loaded with 50 $\Omega$ Thevenin |      |         |      |      |

|        |                                             | termination and 20pF                |                                       |      |         |      |      |

|        |                                             |                                     |                                       |      |         |      |      |

NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 3.3V, +25°C ambient.

3. Per TTL driven input. All other inputs at Vcc or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations. It is derived with Q frequency as the reference.

5. Values for these conditions are examples of the Icc formula. These limits are guaranteed but not tested.

6. IC = IQUIESCENT + INPUTS + IDYNAMIC

IC = ICC + DICC DHNT + ICCD (f) + ILOAD

Icc = Quiescent Current (IccL, IccH and Iccz)

$\Delta$ Icc = Power Supply Current for a TTL High Input (VIN = 3.4V)

DH = Duty Cycle for TTL Inputs High

NT = Number of TTL Inputs at DH

ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

f = 2Q Frequency

ILOAD = Dynamic Current due to load.

## SYNCH INPUT TIMING REQUIRMENTS

| Symbol     | Parameter                     | Min.              | Max.    | Unit |

|------------|-------------------------------|-------------------|---------|------|

| TRISE/FALL | Rise/Fall Times, SYNC inputs  | _                 | 3       | ns   |

|            | (0.8V to 2V)                  |                   |         |      |

| Frequency  | Input Frequency, SYNC Inputs  | 10 <sup>(1)</sup> | 2Q fmax | MHz  |

| Duty Cycle | Input Duty Cycle, SYNC Inputs | 25%               | 75%     | _    |

## OUTPUT FREQUENCY SPECIFICATIONS

|        |                                                    |      |      | Max. <sup>(2)</sup> |                    |                           |      |

|--------|----------------------------------------------------|------|------|---------------------|--------------------|---------------------------|------|

| Symbol | Parameter                                          | Min. | 70   | 100                 | 133 <sup>(3)</sup> | <b>150</b> <sup>(3)</sup> | Unit |

| f2Q    | Operating frequency 2Q Output                      | 40   | 70   | 100                 | 133                | 150                       | MHz  |

| fQ     | Operating frequency Q0-Q4, $\overline{Q}5$ Outputs | 20   | 35   | 50                  | 66.7               | 75                        | MHz  |

| fQ/2   | Operating frequency Q/2 Output                     | 10   | 17.5 | 25                  | 33.3               | 37.5                      | MHz  |

NOTES:

1. Note 7 in "General AC Specification Notes" and Figure 3 describes this specification and its actual limits depending on the feedback connection.

2. Maximum operating frequency is guaranteed with the part in a phase locked condition and all outputs loaded.

3. At this frequency, 2Q cannot be used as feedback.

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE

| Symbol                                         | Parameter                                        | Condition <sup>(1)</sup>                        | Min.                         | Max.                           | Unit |

|------------------------------------------------|--------------------------------------------------|-------------------------------------------------|------------------------------|--------------------------------|------|

| trise/fall                                     | Rise/Fall Time                                   | Load = $50\Omega$ to Vcc/2, CL = $20pF$         | 0.2 <sup>(2)</sup>           | 2                              | ns   |

| All Outputs                                    | (between 0.8V and 2V)                            |                                                 |                              |                                |      |

| tPULSE WIDTH <sup>(3)</sup>                    | Output Pulse Width                               | Load = $50\Omega$ to Vcc/2, CL = $20pF$         | 0.5tcycle-0.8 <sup>(5)</sup> | 0.5tcycle + 0.8 <sup>(5)</sup> | ns   |

| Q, $\overline{Q}$ , Q/2 outputs <sup>(3)</sup> | Q0-Q4, Q                                         |                                                 |                              |                                |      |

| <b>t</b> PULSE WIDTH                           | Output Pulse Width                               |                                                 | 0.5tcycle-1 <sup>(5)</sup>   | 0.5tcycle + 1 <sup>(5)</sup>   | ns   |

| 2QOutput <sup>(3)</sup>                        | 2Q @ 1.5V                                        |                                                 |                              |                                |      |

| tPD                                            | SYNC input to FEEDBACK delay                     | Load = $50\Omega$ to Vcc/2, CL = $20pF$         | +0.3                         | +1.3                           | ns   |

| SYNC-FEEDBACK <sup>(3)</sup>                   | (measured at SYNC0 or 1 and FEEDBACK input pins) | $0.1\mu F$ from LF to Analog GND <sup>(5)</sup> |                              |                                |      |

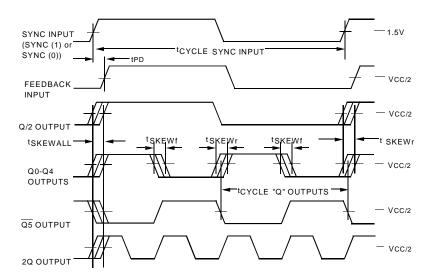

| tskewr                                         | Output to Output Skew between outputs 2Q, Q0-Q4, | Load = $50\Omega$ to Vcc/2, CL = $20pF$         | —                            | 600                            | ps   |

| (rising) <sup>(3,4)</sup>                      | Q/2 (rising edges only)                          |                                                 |                              |                                |      |

| tskewf                                         | Output to Output Skew                            |                                                 | —                            | 250                            | ps   |

| (falling) <sup>(3,4)</sup>                     | between outputs Q0-Q4 (falling edges only)       |                                                 |                              |                                |      |

| tskewall <sup>(3,4)</sup>                      | Output to Output Skew                            |                                                 | —                            | 800                            | ps   |

|                                                | 2Q, Q/2, Q0-Q4 rising, $\overline{Q}5$ falling   |                                                 |                              |                                |      |

| tLOCK <sup>(6)</sup>                           | Time required to acquire Phase-Lock from time    |                                                 | 1 <sup>(2)</sup>             | 10                             | ms   |

|                                                | SYNC input signal is received                    |                                                 |                              |                                |      |

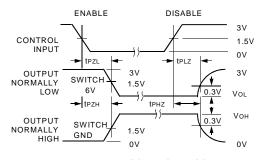

| tрzн                                           | Output Enable Time                               |                                                 | 3(2)                         | 14                             | ns   |

| tPZL                                           | OE/RST (LOW-to-HIGH) to Q, 2Q, Q/2, Q            |                                                 |                              |                                |      |

| <b>t</b> PHZ                                   | Output Disable Time                              | 1                                               | 3(2)                         | 14                             | ns   |

| <b>t</b> PLZ                                   | OE/RST (HIGH-to-LOW) to Q, 2Q, Q/2, Q            |                                                 |                              |                                |      |

### GENERAL AC SPECIFICATION NOTES:

- 1. See test circuit and waveforms.

- 2. Minimum limits are guaranteed but not tested.

- 3. These specifications are guaranteed but not production tested.

- 4. Under equally loaded conditions, as specified under test conditions and at a fixed temperature and voltage.

- 5. tcycle = 1/frequency at which each output (Q,  $\overline{Q}$ , Q/2 or 2Q) is expected to run.

- 6. With Vcc fully powered-on and an output properly connected to the FEEDBACK pin, tLock Max. is with C1 = 0.1µF, tLock Min. is with C1 = 0.01µF. (Where C1 is loop filter capacitor shown in Figure 2).

- 7. The wiring diagrams and written explanations of Figure 3 demonstrate the input and output frequency relationships for various possible feedback configurations. The allowable SYNC input range to stay in the phase-locked condition is also indicated. There are two allowable SYNC frequency ranges, depending on whether FREQ\_SEL is HIGH or LOW. Also it is possible to feed back the  $\overline{Q5}$  output, thus creating a 180° phase shift between the SYNC input and the Q outputs. The table below summarizes the allowable SYNC frequency range for each possible configuration.

| FREQ_SEL | Feedback      | Allowable SYNC Input     | Corresponding 2Q Output | Phase Relationship of the Q Outputs |

|----------|---------------|--------------------------|-------------------------|-------------------------------------|

| Level    | Output        | Frequency Range (MHZ)    | Frequency Range         | to Rising SYNC Edge                 |

| HIGH     | Q/2           | 10 to (2x_Q fмах Spec)/4 | 40 to (2Q fmax Spec)    | 0°                                  |

| HIGH     | Any Q (Q0-Q4) | 20 to (2x_Q fmax Spec)/2 | 40 to (2Q fmax Spec)    | 0°                                  |

| HIGH     | <u>Q5</u>     | 20 to (2x_Q fmax Spec)/2 | 40 to (2Q fmax Spec)    | 180°                                |

| HIGH     | 2X_Q          | 40 to (2x_Q fmax Spec)   | 40 to (2Q fmax Spec)    | 0°                                  |

| LOW      | Q/2           | 5 to (2x_Q fmax Spec)/8  | 20 to (2Q fmax Spec)/2  | 0°                                  |

| LOW      | Any Q (Q0-Q4) | 10 to (2x_Q fмах Spec)/4 | 20 to (2Q fmax Spec)/2  | 0°                                  |

| LOW      | <u>Q5</u>     | 10 to (2x_Q fмах Spec)/4 | 20 to (2Q fmax Spec)/2  | 180°                                |

| LOW      | 2X_Q          | 20 to (2x_Q fmax Spec)/2 | 20 to (2Q fmax Spec)/2  | 0°                                  |

#### GENERAL AC SPECIFICATION NOTES (continued):

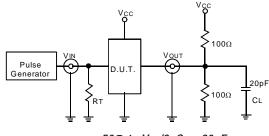

8. The tPD spec describes how the phase offset between the SYNC input and the output connected to the FEEDBACK input, varies with process, temperature and voltage. The phase measurements were made at 1.5V. The Q/2 output was terminated at the FEEDBACK input with 100Ω to Vcc and 100Ω to ground. tPD measurements were made with the loop filter connection shown in Figure 1 below:

Figure 1

#### NOTES:

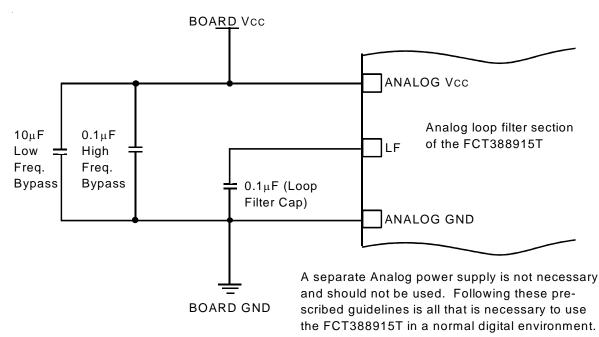

- 1. Figure 2 shows a loop filter and analog isolation scheme which will be effective in most applications. The following guidelines should be followed to ensure stable and jitter-free operation:

- a. All loop filter and analog isolation components should be tied as close to the package as possible. Stray current passing through the parasitics of long traces can cause undesirable voltage transients at the LF pin.

- b. The 10µF low frequency bypass capacitor and the 0.1µF high frequency bypass capacitor form a wide bandwidth filter that will minimize the 388915T's sensitivity to voltage transients from the system digital Vcc supply and ground planes.

If good bypass techniques are used on a board design near components which may cause digital Vcc and ground noise, Vcc step deviations should not occur at the 388915T's digital Vcc supply. The purpose of the bypass filtering scheme shown in figure 2 is to give the 388915T additional protection from the power supply and ground plane transients that can occur in a high frequency, high speed digital system.

- c. The loop filter capacitor (0.1µF) can be a ceramic chip capacitor, the same as a standard bypass capacitor.

- 2. In addition to the bypass capacitors used in the analog filter of Figure 2 there should be a 0.1µF bypass capacitor between each of the other (digital) four Vcc pins and the board ground plane. This will reduce output switching noise caused by the 388915T outputs, in addition to reducing potential for noise in the "analog" section of the chip. These bypass capacitors should also be tied as close to the 388915T package as possible.

Figure 2. Recommended Loop Filter and Analog Isolation Scheme for the FCT388915T

COMMERCIALTEMPERATURERANGE

The frequency relationship shown here is applicable to all Q outputs (Q0, Q1, Q2, Q3 and Q4).

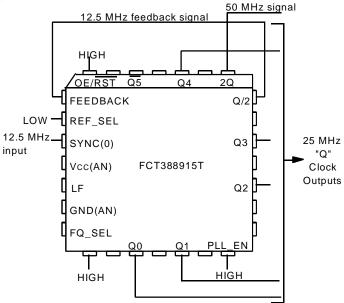

### 1:2 INPUT TO "Q" OUTPUT FREQUENCY RELATIONSHIP

In this application, the Q/2 output is connected to the FEEDBACK input. The internal PLL will line up the positive edges of Q/2 and SYNC, thus the Q/2 frequency will equal the SYNC frequency. The Q outputs (Q0-Q4,  $\overline{\text{Q5}}$ ) will always run at 2X the Q/2 frequency, and the 2Q output will run at 4X the Q/2 frequency.

Allowable Input Frequency Range: 10MHz to (f2Q MAX Spec)/4 (for FREQ\_SEL HIGH) 5MHz to (f2Q MAX Spec)/8 (for FREQ\_SEL LOW)

Figure 3a. Wiring Diagram and Frequency Relationships With Q/ 2 Output Feedback

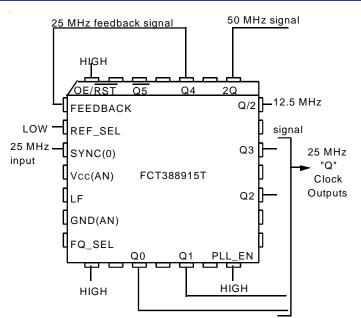

## 1:1 INPUT TO "Q" OUTPUT FREQUENCY RELATIONSHIP

In this application, the Q4 output is connected to the FEEDBACK input. The internal PLL will line up the positive edges of Q4 and SYNC, thus the Q4 frequency (and the rest of the "Q" outputs) will equal the SYNC frequency. The Q/2 output will always run at 1/2 the Q frequency, and the 2Q output will run at 2X the Q frequency.

Allowable Input Frequency Range:

20MHz to (f2Q MAX Spec)/2 (for FREQ\_SEL HIGH) 10MHz to (f2Q MAX Spec)/4 (for FREQ\_SEL LOW)

### Figure 3b. Wiring Diagram and Frequency Relationships With Q4 Output Feedback

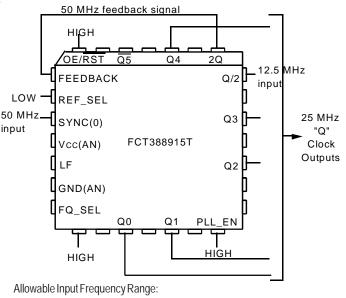

## 2:1 INPUT TO "Q" OUTPUT FREQUENCY RELATIONSHIP

In this application, the 2Q output is connected to the FEEDBACK input. The internal PLL will line up the positive edges of 2Q and SYNC, thus the 2Q frequency will equal the SYNC frequency. The Q/2 output will always run at 1/4 the 2Q frequency, and the Q output will run at 1/2 the 2Q frequency.

40MHz to (f2Q MAX Spec) (for FREQ\_SEL HIGH) 20MHz to (f2Q MAX Spec)/2 (for FREQ\_SEL LOW)

Figure 3c. Wiring Diagram and Frequency Relationships With 2Q Output Feedback

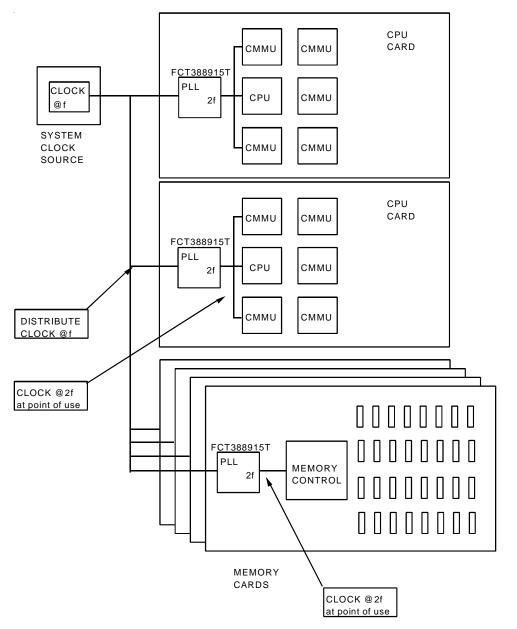

Figure 4. Multiprocessing Application Using the FCT388915T for Frequency Multiplication and Low Board-to-Board skew

## FCT388915TSYSTEMLEVELTESTING FUNCTIONALITY

When the PLL\_EN pin is LOW, the PLL is bypassed and the FCT388915T is in low frequency "test mode". In test mode (with FREQ\_SEL HIGH), the 2Q output is inverted from the selected SYNC input, and the Q outputs are divideby-2 (negative edge triggered) of the SYNC input, and the Q/2 output is divideby-4 (negative edge triggered). With FREQ\_SEL LOW the 2Q output is divideby-2 of the SYNC, the Q outputs divide-by-4, and the Q/2 output divide-by-8. These relationships can be seen in the block diagram. A recommended test configuration would be to use SYNC0 or SYNC1 as the test clock input, and tie PLL\_EN and REF\_SEL together and connect them to the test select logic.

This functionality is needed since most board-level testers run at 1 MHz or below, and the FCT 388915T cannot lock onto that low of an input frequency. In the test mode described above, any test frequency test can be used.

### TEST CIRCUITS AND WAVEFORMS

50 $\Omega$  to Vcc/2, CL = 20pF

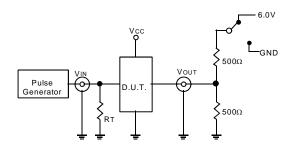

Enable and Disable Test Circuit

Propagation Delay, Output Skew

#### (These waveforms represent the configuration of Figure 3a)

#### NOTES:

- 1. The FCT388915T aligns rising edges of the FEEDBACK input and SYNC input, therefore the SYNC input does not require a 50% duty cycle.

- All skew specs are measured between the Vcc/2 crossing point of the appropriate output edges. All skews are specified as "windows", not as ± deviation around a center point.

If a Q ouput is connected to the FEEDBACK input (this situation is not shown), the Q output frequency would match the SYNC input frequency, the 2Q output would run at twice the SYNC frequency and the Q/2 output would run at half the SYNC frequency.

Enable and Disable Times

### NOTES:

- 1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH.

- 2. Pulse Generator for All Pulses: tF  $\leq$  2.5ns; tR  $\leq$  2.5ns.

### **SWITCH POSITION**

| Test                        | Switch |

|-----------------------------|--------|

| Disable Low<br>Enable Low   | 6V     |

| Disable High<br>Enable High | GND    |

#### **DEFINITIONS:**

CL = Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

### ORDERING INFORMATION

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 *for SALES:* 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com for Tech Support: logichelp@idt.com (408) 654-6459